二、RTL级低功耗设计(续)

前面一篇博文我记录了操作数隔离等低功耗设计,这里就主要介绍一下使用门控时钟进行低功耗设计。

(4)门控时钟

门控时钟在我的第一篇博客中有简单的描述,这里就进行比较详细的描述吧。我们主要学习门控时钟电路是什么、什么使用门控时钟、综合库里的门控时钟、如何使用门控时钟、对门控时钟的一些处理、手动插入门控时钟。我们重点介绍如何使用门控时钟和门控时钟的处理。

①门控时钟概述

门控时钟有两种方案:一种直接针对寄存器的时钟进行门控,一种对模块级别的时钟进行门控。相比之下,直接对寄存器的时钟进行门控更为灵活。因为在很多时候,我们不能保证刚好将不需要门控的寄存器与需要门控的寄存器分配在不同的模块。因此我们主要介绍寄存器级的门控时钟。

=============================================================================

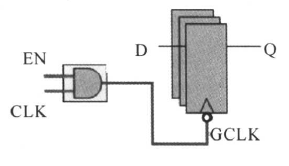

下图是门控时钟的一个简单电路图:

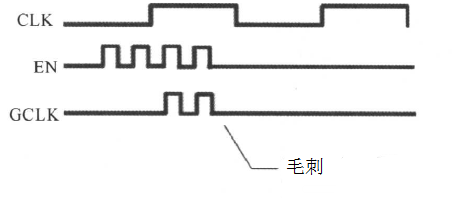

上述电路图中,将控制信号(EN)直接与时钟信号(CLK)进行与操作,以完成门控。门控后的时钟信号GCLK送到寄存器阵列中。这样,当EN为0时,该时钟被关掉。相应的波形如下所示:

可以看出,如果EN信号不加控制,会导致门控时钟信号出现毛刺。时钟上的信号出现毛刺是非常危险的。所以在进行门控时,为了使门控时钟不产生毛刺,使能信号必须满足条件:

延伸阅读

学习是年轻人改变自己的最好方式

学习是年轻人改变自己的最好方式